Table of Contents

Xilinx ML401

Manufacturer

Manuals

Description

- Devices Supported: XC4VLX25-FF668-10C

- Clocks: 100 MHz Oscillator, 2 Clock Sockets

- Memory: 64 MB DDR SDRAM, 8Mb ZBT SRAM, 64 Mb Flash, 4 kb IIC EEPROM

- Display: 16 x2 Character LCD

- Connectors and Interfaces: 4 SMA Connectors (Differential Clocks), 2 PS/2 Connectors (Keyboard/Mouse), 4 Audio Jacks (Line In/Out, Microphone, Head Phone)

- RS-232 Serial Port, 3 USB Ports (2 Peripheral/1 Host), PC4 JTAG, DB 15 VGA

- Xilinx Devices on Board: XC4VLX25-FF668-10C, XC95144XL, XCCACE (System ACE™ CF), XCF32P (Platform Flash)

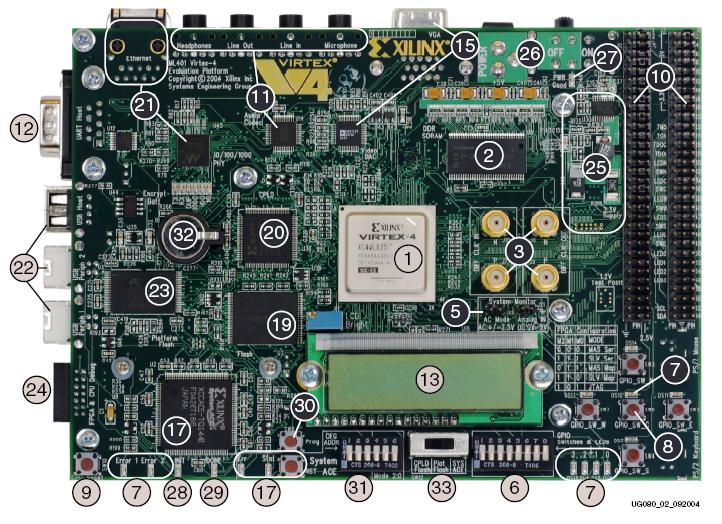

Board pictures

Describe fotos:

- FPGA XC4VLX25-FF668-10C

- 64MB DDR

- Differential Clock Input And Output With SMA Connectors

- Oscillator socket

- System monitor

- DIP Switches

- User & Error Leds

- User push buttons

- CPU reset buttons

- Expansion Headers - IIC,JTAG

- Stereo AC97 audio codec- National Semiconductor LM4550

- RS-232 Serial Port

- 16-Character x 2-Line LCD-(Lumex LCM-S01602DTR/M)

- IIC Bus with 4-kb EEPROM (Microchip Technology 24LC04B-I/ST)

- VGA Output

- PS/2 Mouse and Keyboard Ports

- System ACE and CompactFlash Connector

- A blinking red error LED indicates that no CompactFlash card is present

- A solid red error LED indicates an error condition during configuration

- A blinking green status LED indicates a configuration operation is ongoing

- A solid green status LED indicates a successful download

- ZBT Synchronous SRAM (Cypress CY7C1354B) 256K x 36 bits.

- Linear Flash Memory Chips (Micron MT28F320J3RG-11 ET) 8MB

- Xilinx XC95144XL CPLD - connected to FLASH

- 10/100/1000 Tri-Speed Ethernet PHY Marvell Alaska PHY device (88E1111)

- USB Controller with Host and Peripheral Ports Cypress CY7C67300

- The firmware for this processor can be stored in its own dedicated IIC EEPROM (U17), download via J27

- Xilinx XCF32P Platform Flash Configuration Storage Device

- The Platform Flash memory can be used to program the FPGA using master or slave configuration in serial or parallel (SelectMap) modes. The board is wired up so the Platform Flash memory can download bitstreams in Master Serial, Slave Serial, Master SelectMAP (parallel), or Slave SelectMAP (parallel) modes. Using the iMPACT tool to program the Platform Flash memory, the user has the option to select which of the four modes to use for programming the FPGA. The configuration mode DIP switches on the board must be set to match the programming method being used by the Platform Flash memory.

- JTAG Configuration Port

- On-Board Power Supplies

- AC Adapter and Input Power Switch/Jack

- Power Indicator LED

- INIT LED

- DONE LED- status on DONE pin FPGA

- Program Switch

- Configuration Address and Mode DIP Switches

M2 M1 M0 Mode 0 0 0 Master Serial 1 1 1 Slave Serial 0 1 1 Master Parallel (SelectMAP) 1 1 0 Slave Parallel (SelectMAP) 1 0 1 JTAG 32 Encryption Key Battery 33 Configuration Source Selector Switch

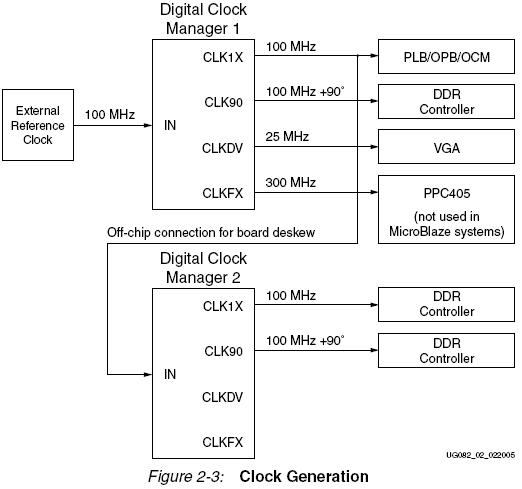

Clock distribution

JTAG interface - schematic

Impact

Internal architecture FPGA

Kernel Log

========================= Xilinx ML401 Flash Loader ========================= Succesfully finished. Jump to kernel ... Linux version 2.4.29-uc0 (root@monstrunix) (gcc version 2.95.3-4 Xilinx EDK 6.3 Build EDK_Gmm.12.2) #25 Po Dec 18 13:30:52 CEST 2005 On node 0 totalpages: 16384 zone(0): 16384 pages. zone(1): 0 pages. zone(2): 0 pages. CPU: MICROBLAZE Kernel command line: ° Console: xmbserial on UARTLite Calibrating delay loop... 32.87 BogoMIPS Memory: 64MB = 64MB total Memory: 62336KB available (1365K code, 1120K data, 44K init) Dentry cache hash table entries: 8192 (order: 4, 65536 bytes) Inode cache hash table entries: 4096 (order: 3, 32768 bytes) Mount cache hash table entries: 512 (order: 0, 4096 bytes) Buffer cache hash table entries: 4096 (order: 2, 16384 bytes) Page-cache hash table entries: 16384 (order: 4, 65536 bytes) POSIX conformance testing by UNIFIX Linux NET4.0 for Linux 2.4 Based upon Swansea University Computer Society NET3.039 Initializing RT netlink socket Microblaze UARTlite serial driver version 1.00 ttyS0 at 0xa0000000 (irq = 10) is a Microblaze UARTlite Starting kswapd Journalled Block Device driver loaded xgpio #0 at 0x90000000 mapped to 0x90000000 xgpio #1 at 0x90001000 mapped to 0x90001000 xgpio #2 at 0x90002000 mapped to 0x90002000 Xilinx GPIO registered RAMDISK driver initialized: 16 RAM disks of 4096K size 1024 blocksize Initializing SystemAce driver Partition check: xsysacea: unknown partition table System ACE at 0xCF000000 mapped to 0xCF000000, irq=4, 31360KB eth0: using fifo mode. eth0: Xilinx EMAC #0 at 0x60000000 mapped to 0x60000000, irq=2 eth0: id 2.0h; block id 7, type 1 uclinux[mtd]: RAM probe address=0x10192a5c size=0xdb000 uclinux[mtd]: root filesystem index=0 MBVanilla flash probe(0x28000000,8388608,4): 800000 at 28000000 cfi_cmdset_0001: Erase suspend on write enabled 0: offset=0x0,size=0x40000,blocks=32 Using buffer write method Creating 10 MTD partitions on "Flash": 0x00000000-0x00100000 : "fpga0" 0x00100000-0x00200000 : "fpga1" 0x00200000-0x00240000 : "Bootloader" 0x00240000-0x00280000 : "Bootargs" 0x00280000-0x002c0000 : "MAC" 0x002c0000-0x00340000 : "Config" 0x00340000-0x00400000 : "Spare" 0x00400000-0x00700000 : "Image" 0x00700000-0x00800000 : "JFFS2" 0x00000000-0x00800000 : "Flash" MBVanilla ram probe(0x10192a5c,897024,4): db000 at 10192a5c Creating 1 MTD partitions on "RAM": 0x00000000-0x000db000 : "Romfs" NET4: Linux TCP/IP 1.0 for NET4.0 IP Protocols: ICMP, UDP, TCP IP: routing cache hash table of 512 buckets, 4Kbytes TCP: Hash tables configured (established 4096 bind 4096) NET4: Unix domain sockets 1.0/SMP for Linux NET4.0. FAT: bogus logical sector size 62368 UMSDOS: msdos_read_super failed, mount aborted. FAT: bogus logical sector size 62368 FAT: bogus logical sector size 62368 VFS: Mounted root (romfs filesystem) readonly. Freeing init memory: 44K Mounting proc: Mounting var: Populating /var: Running local start scripts. Mounting /etc/config: Populating /etc/config: flatfsd: Created 4 configuration files (353 bytes) Setting hostname: Setting up interface lo: Starting DHCP client: Starting inetd: Starting thttpd: ML401 login: root Password: